1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

311

312

313

314

315

316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

332

333

334

335

336

337

338

339

340

341

342

343

344

345

346

347

348

349

350

351

352

353

354

355

356

357

358

359

360

361

362

363

364

|

---

layout: docs

title: "Deep Dive into Connection Operators"

section: "chisel3"

---

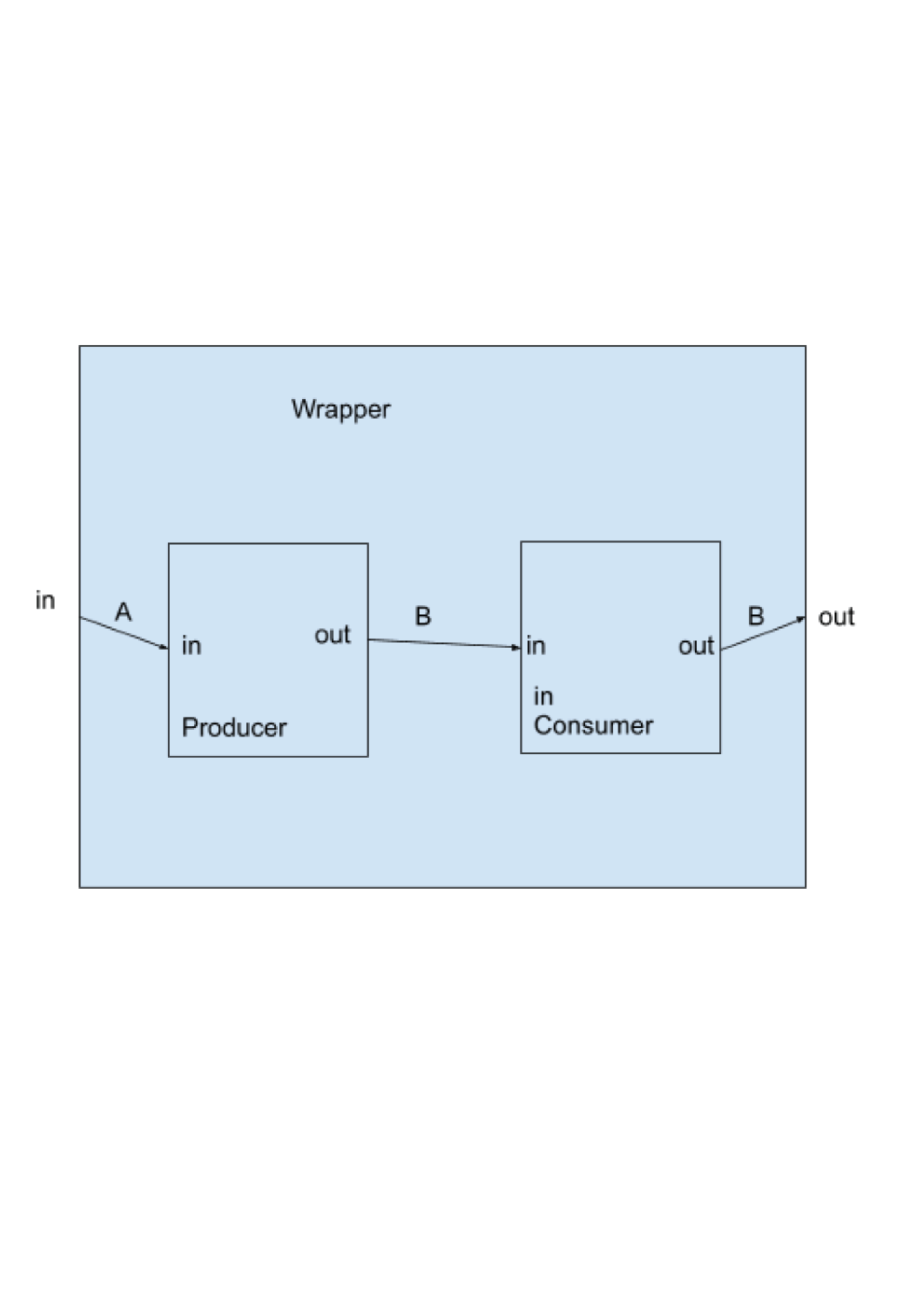

# Deep Dive into Connection Operators

Chisel contains two connection operators, `:=` and `<>`. This document provides a deeper explanation of the differences of the two and when to use one or the other. The differences are demonstrated with experiments using Scastie examples which use `DecoupledIO`.

### Experiment Setup

```scala mdoc

// Imports used by the following examples

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

```

The diagram for the experiment can be viewed [here](https://docs.google.com/document/d/14C918Hdahk2xOGSJJBT-ZVqAx99_hg3JQIq-vaaifQU/edit?usp=sharing).

```scala mdoc:silent

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(DecoupledIO(UInt(8.W)))

val out = DecoupledIO(UInt(8.W))

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

// connect Producer to IO

p.io.a <> io.in

// connect producer to consumer

c.io.a <> p.io.b

// connect consumer to IO

io.out <> c.io.b

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.b <> io.a

}

```

Below we can see the resulting Verilog for this example:

```scala mdoc

ChiselStage.emitVerilog(new Wrapper)

```

## Concept 1: `<>` is Commutative

This experiment is set up to test for the function of `<>` using the experiment above.

Achieving this involves flipping the RHS and LHS of the `<>` operator and seeing how `<>` will react.

( Scastie link for the experiment:https://scastie.scala-lang.org/Shorla/LVhlbkFQQnq7X3trHfgZZQ )

```scala mdoc:silent:reset

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(DecoupledIO(UInt(8.W)))

val out = DecoupledIO(UInt(8.W))

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

// connect producer to I/O

io.in <> p.io.a

// connect producer to consumer

p.io.b <> c.io.a

// connect consumer to I/O

c.io.b <> io.out

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.a <> io.b

}

```

Below we can see the resulting Verilog for this example:

```scala mdoc

ChiselStage.emitVerilog(new Wrapper)

```

### Conclusion:

The Verilog remained the same without incurring errors, showing that the `<>` operator is commutative.

## Concept 2: `:=` means assign ALL LHS signals from the RHS, regardless of the direction on the LHS.

Using the same experiment code as above, we set to test for the function of `:=`

We replace all instances of `<>` with `:=` in the sample code above.

(Scastie link to the experiment: https://scastie.scala-lang.org/Shorla/o1ShdaY3RWKf0IIFwwQ1UQ/1)

```scala mdoc:silent:reset

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(DecoupledIO(UInt(8.W)))

val out = DecoupledIO(UInt(8.W))

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

// connect producer to I/O

p.io.a := io.in

// connect producer to consumer

c.io.a := p.io.b

// connect consumer to I/O

io.out := c.io.b

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.a := io.b

}

```

Below we can see the resulting error message for this example:

```scala mdoc:crash

ChiselStage.emitVerilog(new Wrapper)

```

### Conclusion:

The := operator goes field-by-field on the LHS and attempts to connect it to the same-named signal from the RHS. If something on the LHS is actually an Input, or the corresponding signal on the RHS is an Output, you will get an error as shown above.

## Concept 3: Always Use `:=` to assign DontCare to Wires

When assigning `DontCare` to something that is not directioned, should you use `:=` or `<>`?

We will find out using the sample codes below:

( Scastie link for the experiment:https://scastie.scala-lang.org/Shorla/ZIGsWcylRqKJhZCkKWlSIA/1)

```scala mdoc:silent:reset

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(DecoupledIO(UInt(8.W)))

val out = DecoupledIO(UInt(8.W))

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

//connect Producer to IO

io.in := DontCare

p.io.a <> DontCare

val tmp = Wire(Flipped(DecoupledIO(UInt(8.W))))

tmp := DontCare

p.io.a <> io.in

// connect producer to consumer

c.io.a <> p.io.b

//connect consumer to IO

io.out <> c.io.b

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.b <> io.a

}

```

Below we can see the resulting Verilog for this example:

```scala mdoc

ChiselStage.emitVerilog(new Wrapper)

```

### Conclusion:

If `<>` were used to assign the unidrectioned wire `tmp` to DontCare, we would get an error. But in the example above, we used `:=` and no errors occurred.

But when `:=` was used to assign the wire to DontCare, no errors will occur.

Thus, when assigning `DontCare` to a `Wire`, always use `:=`.

## Concept 4: You can use `<>` or `:=` to assign `DontCare` to directioned things (IOs)

When assigning `DontCare` to something that is directioned, should you use `:=` or `<>`?

We will find out using the sample codes below:

( Scastie link for the experiment:https://scastie.scala-lang.org/Shorla/ZIGsWcylRqKJhZCkKWlSIA/1)

```scala mdoc:silent:reset

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(DecoupledIO(UInt(8.W)))

val out = DecoupledIO(UInt(8.W))

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

//connect Producer to IO

io.in := DontCare

p.io.a <> DontCare

val tmp = Wire(Flipped(DecoupledIO(UInt(8.W))))

tmp := DontCare

p.io.a <> io.in

// connect producer to consumer

c.io.a <> p.io.b

//connect consumer to IO

io.out <> c.io.b

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.b <> io.a

}

```

Below we can see the resulting Verilog for this example:

```scala mdoc

ChiselStage.emitVerilog(new Wrapper)

```

### Conclusion:

Both `<>` and `:=` can be used to assign directioned things (IOs) to DontCare as shown in `io.in` and `p.io.a` respectively. This is basically equivalent because in this case both `<>` and `:=` will determine the direction from the LHS.

## Concept 5: `<>` works between things with at least one known flow (An IO or child's IO).

If there is at least one known flow what will `<>` do? This will be shown using the experiment code below:

( Scastie link for the experiment:https://scastie.scala-lang.org/Shorla/gKx9ReLVTTqDTk9vmw5ozg)

```scala mdoc:silent:reset

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(DecoupledIO(UInt(8.W)))

val out = DecoupledIO(UInt(8.W))

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

//connect Producer to IO

// For this experiment, we add a temporary wire and see if it works...

//p.io.a <> io.in

val tmp = Wire(DecoupledIO(UInt(8.W)))

// connect intermediate wire

tmp <> io.in

p.io.a <> tmp

// connect producer to consumer

c.io.a <> p.io.b

//connect consumer to IO

io.out <> c.io.b

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.b <> io.a

}

```

Below we can see the resulting Verilog for this example:

```scala mdoc

ChiselStage.emitVerilog(new Wrapper)

```

### Conclusion:

The connection above went smoothly with no errors, this goes to show `<>` will work as long as there is at least one directioned thing (IO or submodule's IO) to "fix" the direction.

## Concept 6: `<>` and `:=` connect signals by field name.

This experiment creates a MockDecoupledIO which has the same fields by name as a DecoupledIO. Chisel lets us connect it and produces the same verilog, even though MockDecoupledIO and DecoupledIO are different types.

( Scastie link for the experiment:https://scastie.scala-lang.org/Uf4tQquvQYigZAW705NFIQ)

```scala mdoc:silent:reset

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

class MockDecoupledIO extends Bundle {

val valid = Output(Bool())

val ready = Input(Bool())

val bits = Output(UInt(8.W))

}

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(new MockDecoupledIO())

val out = new MockDecoupledIO()

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

// connect producer to I/O

p.io.a <> io.in

// connect producer to consumer

c.io.a <> p.io.b

// connect consumer to I/O

io.out <> c.io.b

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.a <> io.b

}

```

Below we can see the resulting Verilog for this example:

```scala mdoc

ChiselStage.emitVerilog(new Wrapper)

```

And here is another experiment, where we remove one of the fields of MockDecoupledIO:

( Scastie link for the experiment:https://scastie.scala-lang.org/ChtkhKCpS9CvJkjjqpdeIA)

```scala mdoc:silent:reset

import chisel3._

import chisel3.stage.ChiselStage

import chisel3.util.DecoupledIO

class MockDecoupledIO extends Bundle {

val valid = Output(Bool())

val ready = Input(Bool())

//val bits = Output(UInt(8.W))

}

class Wrapper extends Module{

val io = IO(new Bundle {

val in = Flipped(new MockDecoupledIO())

val out = new MockDecoupledIO()

})

val p = Module(new PipelineStage)

val c = Module(new PipelineStage)

// connect producer to I/O

p.io.a <> io.in

// connect producer to consumer

c.io.a <> p.io.b

// connect consumer to I/O

io.out <> c.io.b

}

class PipelineStage extends Module{

val io = IO(new Bundle{

val a = Flipped(DecoupledIO(UInt(8.W)))

val b = DecoupledIO(UInt(8.W))

})

io.a <> io.b

}

```

Below we can see the resulting error for this example:

```scala mdoc:crash

ChiselStage.emitVerilog(new Wrapper)

```

This one fails because there is a field `bits` missing.

### Conclusion:

For `:=`, the Scala types do not need to match but all the signals on the LHS must be provided by the RHS or you will get a Chisel elaboration error. There may be additional signals on the RHS, these will be ignored. For `<>`, the Scala types do not need to match, but all signals must match exactly between LHS and RHS. In both cases, the order of the fields does not matter.

|