diff options

| author | Jack | 2022-03-15 19:37:37 +0000 |

|---|---|---|

| committer | Jack | 2022-03-15 19:37:37 +0000 |

| commit | 2f21943ff772da2171df866d4cee71dfa8127bf8 (patch) | |

| tree | d00c9059c9361920036e784425641288782515d5 /docs/src | |

| parent | 1876e740a48be2e5ff5bd4fd6c2018927f1dcec2 (diff) | |

| parent | f26df23bbe0ae9b7162ed70369f24b01d75a1493 (diff) | |

Merge branch '3.5.x' into 3.5-release

Diffstat (limited to 'docs/src')

| -rw-r--r-- | docs/src/cookbooks/cookbook.md | 141 | ||||

| -rw-r--r-- | docs/src/cookbooks/cookbooks.md | 1 | ||||

| -rw-r--r-- | docs/src/cookbooks/verilog-vs-chisel.md | 833 | ||||

| -rw-r--r-- | docs/src/explanations/connection-operators.md | 2 | ||||

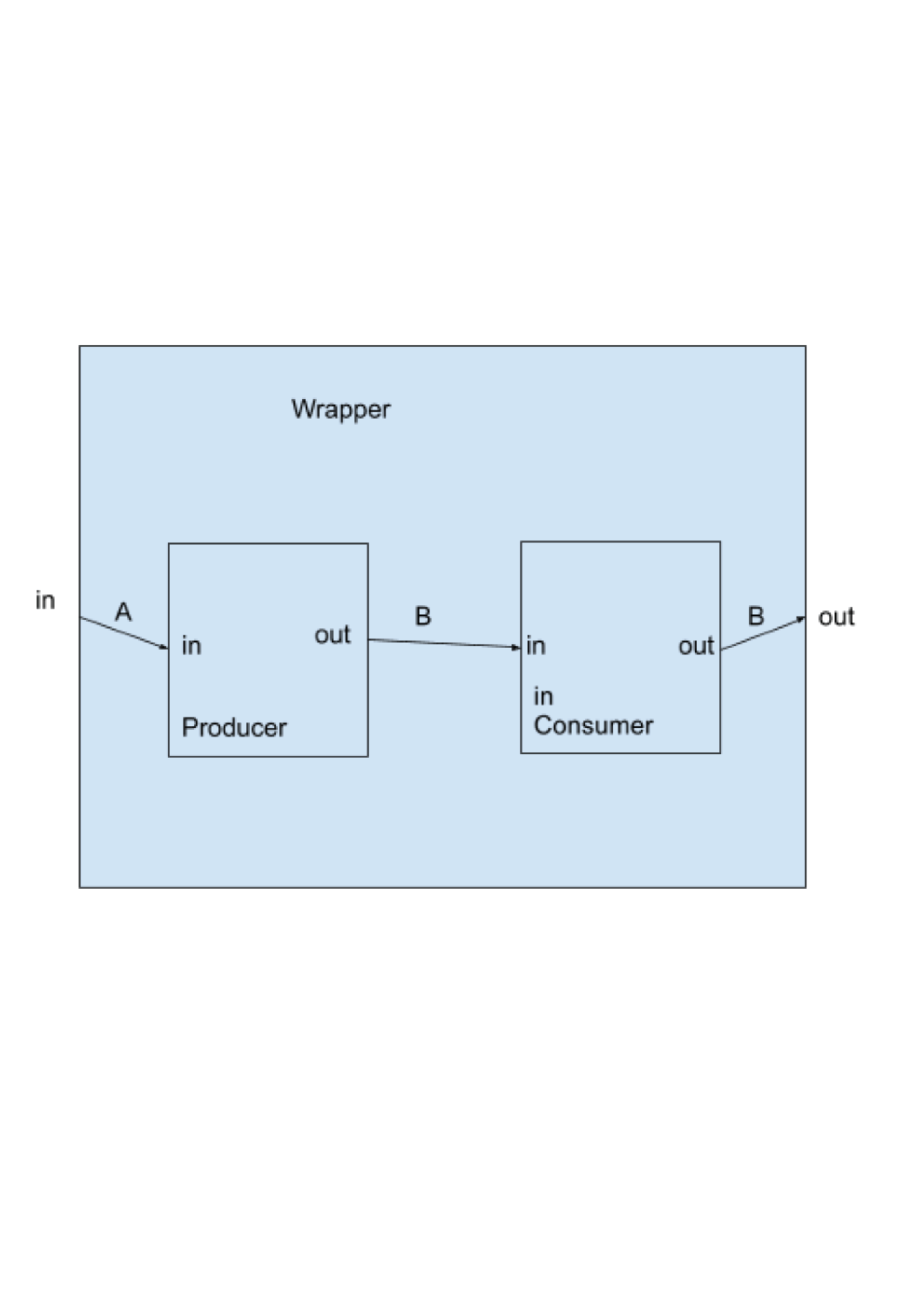

| -rw-r--r-- | docs/src/images/connection-operators-experiment.svg | 1 |

5 files changed, 977 insertions, 1 deletions

diff --git a/docs/src/cookbooks/cookbook.md b/docs/src/cookbooks/cookbook.md index ec7e9ed2..ae7c7bf6 100644 --- a/docs/src/cookbooks/cookbook.md +++ b/docs/src/cookbooks/cookbook.md @@ -20,6 +20,8 @@ Please note that these examples make use of [Chisel's scala-style printing](../e * [Can I make a 2D or 3D Vector?](#can-i-make-a-2D-or-3D-Vector) * [How do I create a Vector of Registers?](#how-do-i-create-a-vector-of-registers) * [How do I create a Reg of type Vec?](#how-do-i-create-a-reg-of-type-vec) +* Bundles + * [How do I deal with aliased Bundle fields?](#aliased-bundle-fields) * [How do I create a finite state machine?](#how-do-i-create-a-finite-state-machine-fsm) * [How do I unpack a value ("reverse concatenation") like in Verilog?](#how-do-i-unpack-a-value-reverse-concatenation-like-in-verilog) * [How do I do subword assignment (assign to some bits in a UInt)?](#how-do-i-do-subword-assignment-assign-to-some-bits-in-a-uint) @@ -231,6 +233,145 @@ class Foo extends RawModule { } ``` +## Bundles + +### <a name="aliased-bundle-fields"></a> How do I deal with aliased Bundle fields? + +```scala mdoc:invisible:reset +import chisel3._ + +class Top[T <: Data](gen: T) extends Module { + val in = IO(Input(gen)) + val out = IO(Output(gen)) + out := in +} +``` + +Following the `gen` pattern when creating Bundles can result in some opaque error messages: + +```scala mdoc +class AliasedBundle[T <: Data](gen: T) extends Bundle { + val foo = gen + val bar = gen +} +``` + +```scala mdoc:crash +getVerilogString(new Top(new AliasedBundle(UInt(8.W)))) +``` + +This error is saying that fields `foo` and `bar` of `AliasedBundle` are the +exact same object in memory. +This is a problem for Chisel because we need to be able to distinguish uses of +`foo` and `bar` but cannot when they are referentially the same. + +Note that the following example looks different but will give you exactly the same issue: + +```scala mdoc +class AlsoAliasedBundle[T <: Data](val gen: T) extends Bundle { + // ^ This val makes `gen` a field, just like `foo` + val foo = gen +} +``` + +By making `gen` a `val`, it becomes a public field of the `class`, just like `foo`. + +```scala mdoc:crash +getVerilogString(new Top(new AlsoAliasedBundle(UInt(8.W)))) +``` + +There are several ways to solve this issue with their own advantages and disadvantages. + +#### 1. 0-arity function parameters + +Instead of passing an object as a parameter, you can pass a 0-arity function (a function with no arguments): + +```scala mdoc +class UsingAFunctionBundle[T <: Data](gen: () => T) extends Bundle { + val foo = gen() + val bar = gen() +} +``` + +Note that the type of `gen` is now `() => T`. +Because it is now a function and not a subtype of `Data`, you can safely make `gen` a `val` without +it becoming a hardware field of the `Bundle`. + +Note that this also means you must pass `gen` as a function, for example: + +```scala mdoc:silent +getVerilogString(new Top(new UsingAFunctionBundle(() => UInt(8.W)))) +``` + +<a name="aliased-warning"></a> **Warning**: you must ensure that `gen` creates fresh objects rather than capturing an already constructed value: + +```scala mdoc:crash +class MisusedFunctionArguments extends Module { + // This usage is correct + val in = IO(Input(new UsingAFunctionBundle(() => UInt(8.W)))) + + // This usage is incorrect + val fizz = UInt(8.W) + val out = IO(Output(new UsingAFunctionBundle(() => fizz))) +} +getVerilogString(new MisusedFunctionArguments) +``` +In the above example, value `fizz` and fields `foo` and `bar` of `out` are all the same object in memory. + + +#### 2. By-name function parameters + +Functionally the same as (1) but with more subtle syntax, you can use [Scala by-name function parameters](https://docs.scala-lang.org/tour/by-name-parameters.html): + +```scala mdoc +class UsingByNameParameters[T <: Data](gen: => T) extends Bundle { + val foo = gen + val bar = gen +} +``` + +With this usage, you do not include `() =>` when passing the argument: + +```scala mdoc:silent +getVerilogString(new Top(new UsingByNameParameters(UInt(8.W)))) +``` + +Note that as this is just syntactic sugar over (1), the [same warning applies](#aliased-warning). + +#### 3. Directioned Bundle fields + +You can alternatively wrap the fields with `Output(...)`, which creates fresh instances of the passed argument. +Chisel treats `Output` as the "default direction" so if all fields are outputs, the `Bundle` is functionally equivalent to a `Bundle` with no directioned fields. + +```scala mdoc +class DirectionedBundle[T <: Data](gen: T) extends Bundle { + val foo = Output(gen) + val bar = Output(gen) +} +``` + +```scala mdoc:invisible +getVerilogString(new Top(new DirectionedBundle(UInt(8.W)))) +``` + +This approach is admittedly a little ugly and may mislead others reading the code because it implies that this Bundle is intended to be used as an `Output`. + +#### 4. Call `.cloneType` directly + +You can also just call `.cloneType` on your `gen` argument directly. +While we try to hide this implementation detail from the user, `.cloneType` is the mechanism by which Chisel creates fresh instances of `Data` objects: + +```scala mdoc +class UsingCloneTypeBundle[T <: Data](gen: T) extends Bundle { + val foo = gen.cloneType + val bar = gen.cloneType +} +``` + +```scala mdoc:invisible +getVerilogString(new Top(new UsingCloneTypeBundle(UInt(8.W)))) +``` + ### How do I create a finite state machine (FSM)? The advised way is to use [`ChiselEnum`](https://www.chisel-lang.org/api/latest/chisel3/experimental/index.html#ChiselEnum=chisel3.experimental.EnumFactory) to construct enumerated types representing the state of the FSM. diff --git a/docs/src/cookbooks/cookbooks.md b/docs/src/cookbooks/cookbooks.md index 7c3eb8b9..9681a1e8 100644 --- a/docs/src/cookbooks/cookbooks.md +++ b/docs/src/cookbooks/cookbooks.md @@ -11,6 +11,7 @@ If you have any requests or examples to share, please [file an issue](https://github.com/chipsalliance/chisel3/issues/new) and let us know! * [General Cookbooks](cookbook) +* [Verilog vs. Chisel Side-by-Side](verilog-vs-chisel) * [Naming Cookbook](naming) * [Troubleshooting Guide](troubleshooting) * [Hierarchy Cookbook](hierarchy) diff --git a/docs/src/cookbooks/verilog-vs-chisel.md b/docs/src/cookbooks/verilog-vs-chisel.md new file mode 100644 index 00000000..1adf609e --- /dev/null +++ b/docs/src/cookbooks/verilog-vs-chisel.md @@ -0,0 +1,833 @@ +--- +layout: docs +title: "Verilog-vs-Chisel" +section: "chisel3" +--- + +<!Doctype html> +<html> + +# Verilog vs Chisel Side-By-Side + +This page serves as a quick introduction to Chisel for those familiar with Verilog. It is by no means a comprehensive guide of everything Chisel can do. Feel free to file an issue with suggestions of things you'd like to see added to this page. + +```scala mdoc:invisible +import chisel3._ +import chisel3.util.{switch, is} +import chisel3.stage.ChiselStage +import chisel3.experimental.ChiselEnum +import chisel3.util.{Cat, Fill, DecoupledIO} +``` + +<body> + <!-- This script is needed so that Markdown and HTML will render together, see link to Stack overflow --> + <script src="https://cdn.mathjax.org/mathjax/latest/MathJax.js?config=TeX-AMS-MML_HTMLorMML" type="text/javascript"></script> + <table border ="0"> + <h1>Creating a Module</h1> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + <tr> +<td> + +```verilog +module Foo ( + input a, + output b +); + assign b = a; +endmodule +``` + +</td> + <td> + +```scala mdoc +class Foo extends Module { + val a = IO(Input(Bool())) + val b = IO(Output(Bool())) + b := a +} +``` +</td> + </tr> + </table> +</body> +</html> + +# Parameterizing a Module + +<html> +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + +<tr> +<td> + +```verilog +module PassthroughGenerator( + input [width-1:0] in, + output [width-1:0] out +); + + parameter width = 8; + + assign out = in; +endmodule +``` +</td> +<td> + +```scala mdoc:silent +class PassthroughGenerator(width: Int = 8) extends Module { + val in = IO(Input(UInt(width.W))) + val out = IO(Output(UInt(width.W))) + + out := in +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new PassthroughGenerator(10)) +``` +</td> + </tr> + <tr> +<td> + +```verilog +module ParameterizedWidthAdder( + input [in0Width-1:0] in0, + input [in1Width-1:0] in1, + output [sumWidth-1:0] sum +); + parameter in0Width = 8; + parameter in1Width = 1; + parameter sumWidth = 9; + + assign sum = in0 + in1; + +endmodule +``` + +</td> +<td> + +```scala mdoc:silent +class ParameterizedWidthAdder( + in0Width: Int, + in1Width: Int, + sumWidth: Int) extends Module { + + val in0 = IO(Input(UInt(in0Width.W))) + val in1 = IO(Input(UInt(in1Width.W))) + val sum = IO(Output(UInt(sumWidth.W))) + + // a +& b includes the carry, a + b does not + sum := in0 +& in1 +} +``` +</td> +</tr> + </table> +<html> +<body> + +# Wire Assignment and Literal Values + +<html> +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> +<tr> +<td> + +```verilog +module MyWireAssignmentModule (); + + wire [31:0] aa = 'd42; + // Logical reg for use in always block, not real register + reg [31:0] a; + + // + always @(*) begin + a = aa; + end + + // Hex value initialization + wire [31:0] b = 32'hbabecafe; + + // Declaration separate from Assignment + wire [15:0] c; + wire d; + + assign c = 16'b1; + assign d = 1'b1; + + // Signed values + wire signed [63:0] g; + assign g = -’d5; + + wire signed [31:0] h = 'd5; + + reg signed[31:0] f; + always@(*) begin + f = ‘d5; + end +endmodule +``` + + +</td> +<td> + +```scala mdoc:silent + + +class MyWireAssignmentModule extends Module { + + val aa = 42.U(32.W) + val a = Wire(UInt(32.W)) + a := aa + val b = "hbabecafe".U(32.W) + val c = Wire(UInt(16.W)) + val d = Wire(Bool()) + c := "b1".U(16.W) + d := true.B + val g = Wire(SInt(64.W)) + g := -5.S + val h = 5.asSInt(32.W) + val f = Wire(SInt(32.W)) + f := 5.S +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new MyWireAssignmentModule) +``` + +</td> +</tr> + </table> +<html> +<body> + +# Register Declaration and Assignment + +<html> +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + <tr> +<td> + +```verilog +module RegisterModule( + input clock, + input reset, + input [7:0] in, + output [7:0] out, + input differentClock, + input differentSyncReset, + input differentAsyncReset +); + + reg [7:0] registerWithoutInit; + reg [7:0] registerWithInit; + reg [7:0] registerOnDifferentClockAndSyncReset; + reg [7:0] registerOnDifferentClockAndAsyncReset; + + + always @(posedge clock) begin + registerWithoutInit <= in + 8'h1; + end + + always @(posedge clock) begin + if (reset) begin + registerWithInit <= 8'd42; + end else begin + registerWithInit <= registerWithInit - 8'h1; + end + end + + always @(posedge differentClock) begin + if (differentSyncReset) begin + registerOnDifferentClockAndSyncReset <= 8'h42; + end else begin + registerOnDifferentClockAndSyncReset <= in - 8'h1; + end + end + + always @(posedge differentClock or posedge differentAsyncReset) begin + if (differentAsyncReset) begin + registerOnDifferentClockAndAsyncReset <= 8'h24; + end else begin + registerOnDifferentClockAndAsyncReset <= in + 8'h2; + end + end + + assign out = in + + registerWithoutInit + + registerWithInit + + registerOnDifferentClockAndSyncReset + + registerOnDifferentClockAndAsyncReset; +endmodule + +``` +</td> +<td> + +```scala mdoc:silent +class RegisterModule extends Module { + val in = IO(Input(UInt(8.W))) + val out = IO(Output(UInt(8.W))) + + val differentClock = IO(Input(Clock())) + val differentSyncReset = IO(Input(Bool())) + + val differentAsyncReset = IO(Input(AsyncReset())) + + val registerWithoutInit = Reg(UInt(8.W)) + + val registerWithInit = RegInit(42.U(8.W)) + + registerWithoutInit := in + 1.U + + registerWithInit := registerWithInit - 1.U + + val registerOnDifferentClockAndSyncReset = withClockAndReset(differentClock, differentSyncReset) { + val reg = RegInit("h42".U(8.W)) + reg + } + registerOnDifferentClockAndSyncReset := in - 1.U + + val registerOnDifferentClockAndAsyncReset = withClockAndReset(differentClock, differentAsyncReset) { + val reg = RegInit("h24".U(8.W)) + reg + } + registerOnDifferentClockAndAsyncReset := in + 2.U + + out := in + + registerWithoutInit + + registerWithInit + + registerOnDifferentClockAndSyncReset + + registerOnDifferentClockAndAsyncReset +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new RegisterModule) +``` +</td> + </tr> + </table> +<html> +<body> + +# Case Statements + +<html> +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + <tr> +<td> + +```verilog +module CaseStatementModule( + input [2:0] a, + input [2:0] b, + input [2:0] c, + input [1:0] sel, + output reg [2:0] out +); + + always @(*) + case (sel) + 2'b00: out <= a; + 2'b01: out <= b; + 2'b10: out <= c; + default: out <= 3'b0; + end + end +endmodule +``` +</td> +<td> + +```scala mdoc:silent +class CaseStatementModule extends Module { + val a, b, c= IO(Input(UInt(3.W))) + val sel = IO(Input(UInt(2.W))) + val out = IO(Output(UInt(3.W))) + + // default goes first + out := 0.U + + switch (sel) { + is ("b00".U) { out := a } + is ("b01".U) { out := b } + is ("b10".U) { out := c } + } +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new CaseStatementModule) +``` +</td> + </tr> + </table> +<html> +<body> + +# Case Statements Using Enums + +<html> +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + <tr> +<td> + +```verilog +module CaseStatementEnumModule1 ( + input [2:0] rs1, + input [2:0] pc, + input AluMux1Sel sel, + output reg [2:0] out); + + typedef enum {SELECT_RS1, SELECT_PC} AluMux1Sel; + + case(sel) + SELECT_RS1: out <= rs1; + SELECT_PC: out <= pc; + default: out <= 3'b0; + end +endmodule +``` +</td> +<td> + +```scala mdoc:silent +class CaseStatementEnumModule1 extends Module { + + object AluMux1Sel extends ChiselEnum { + val selectRS1, selectPC = Value + } + + import AluMux1Sel._ + val rs1, pc = IO(Input(UInt(3.W))) + val sel = IO(Input(AluMux1Sel())) + val out = IO(Output(UInt(3.W))) + + // default goes first + out := 0.U + + switch (sel) { + is (selectRS1) { out := rs1 } + is (selectPC) { out := pc } + } +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new CaseStatementEnumModule1) +``` +</td> + </tr> + <tr> +<td> + +```verilog +module CaseStatementEnumModule2 (input clk); + + typedef enum { + INIT = 3, + IDLE = 'h13, + START = 'h17, + READY = 'h23 } StateValue; + + reg StateValue state; + + + always @(posedge clk) begin + case (state) + IDLE : state = START; + START : state = READY; + READY : state = IDLE ; + default : state = IDLE ; + endcase + end +endmodule +``` +</td> +<td> + +```scala mdoc:silent +class CaseStatementEnumModule2 extends Module { + + object StateValue extends ChiselEnum { + val INIT = Value(0x03.U) + val IDLE = Value(0x13.U) + val START = Value(0x17.U) + val READY = Value(0x23.U) + } + import StateValue._ + val state = Reg(StateValue()) + + + switch (state) { + is (INIT) {state := IDLE} + is (IDLE) {state := START} + is (START) {state := READY} + is (READY) {state := IDLE} + } +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new CaseStatementEnumModule2) +``` +</td> + </tr> + </table> +<html> +<body> + +<!-- +# SystemVerilog Interfaces + +<html> +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + <tr> +<td> + +``` +module MyInterfaceModule( + input clock, + input reset, + output io_in_ready, + input io_in_valid, + input [7:0] io_in_bits, + input io_out_ready, + output io_out_valid, + output [7:0] io_out_bits +); + assign io_in_ready = io_out_ready; // @[main.scala 17:12] + assign io_out_valid = io_in_valid; // @[main.scala 17:12] + assign io_out_bits = io_in_bits; // @[main.scala 17:12] +endmodule +``` +</td> +<td> + +```scala mdoc:silent +class MyInterfaceModule extends Module { +val io = IO(new Bundle { +val in = Flipped(DecoupledIO(UInt(8.W))) +val out = DecoupledIO(UInt(8.W)) +}) + +val tmp = Wire(DecoupledIO(UInt(8.W))) +tmp <> io.in +io.out <> tmp +io.out <> io.in +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new MyInterfaceModule) +``` + +</td> + </tr> + </table> + +<html> +<body> +--> + + +# Multi-Dimensional Memories + +<html> +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + <tr> +<td> + +```verilog +module ReadWriteSmem( + input clock, + input reset, + input io_enable, + input io_write, + input [9:0] io_addr, + input [31:0] io_dataIn, + output [31:0] io_dataOut +); + +reg [31:0] mem [0:1023]; +reg [9:0] addr_delay; + +assign io_dataOut = mem[addr_delay] + + always @(posedge clock) begin + if (io_enable & io_write) begin + mem[io_addr] <= io_data; + end + if (io_enable) begin + addr_delay <= io_addr; + end + end +endmodule +``` +</td> + + +<td> + +```scala mdoc:silent +class ReadWriteSmem extends Module { + val io = IO(new Bundle { + val enable = Input(Bool()) + val write = Input(Bool()) + val addr = Input(UInt(10.W)) + val dataIn = Input(UInt(32.W)) + val dataOut = Output(UInt(32.W)) + }) + + val mem = SyncReadMem(1024, UInt(32.W)) + + // Create one write port and one read port + mem.write(io.addr, io.dataIn) + io.dataOut := mem.read(io.addr, io.enable) +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new ReadWriteSmem) +``` +</td> +</tr> +<tr> +<td> + +```verilog +module ReadWriteMem( + input clock, + input io_enable, + input io_write, + input [9:0] io_addr, + input [31:0] io_dataIn, + output [31:0] io_dataOut + ); + + reg [31:0] mem [0:1023]; + + assign io_dataOut = mem[io_addr]; + + always @(posedge clock) begin + if (io_enable && io_write) begin + mem[io_addr] <= io_dataIn; + end + end + +endmodule +``` + +</td> + +<td> + +```scala mdoc:silent +class ReadWriteMem extends Module { + val io = IO(new Bundle { + val enable = Input(Bool()) + val write = Input(Bool()) + val addr = Input(UInt(10.W)) + val dataIn = Input(UInt(32.W)) + val dataOut = Output(UInt(32.W)) +}) + val mem = Mem(1024, UInt(32.W)) + // Create one write port and one read port + mem.write(io.addr, io.dataIn) + io.dataOut := mem.read(io.addr) +} +``` +```scala mdoc:invisible +ChiselStage.emitVerilog(new ReadWriteMem) +``` +</td> +</tr> + </table> +<html> +<html> + +# Operators + +<body> + <table border ="0"> + <tr> + <td><b style="font-size:30px">Verilog</b></td> + <td><b style="font-size:30px">Chisel</b></td> + </tr> + <tr> +<td> + +```verilog + module OperatorExampleModule( + input clock, + input reset, + input [31:0] x, + input [31:0] y, + input [31:0] c, + output [31:0] add_res, + output [31:0] sub_res, + output [31:0] mod_res, + output [31:0] div_res, + output [31:0] and_res, + output [31:0] or_res, + output [31:0] xor_res, + output [31:0] not_res, + output [31:0] logical_not_res, + output [31:0] mux_res, + output [31:0] rshift_res, + output [31:0] lshift_res, + output andR_res, + output logical_and_res, + output logical_or_res, + output equ_res, + output not_equ_res, + output orR_res, + output xorR_res, + output gt_res, + output lt_res, + output geq_res, + output leq_res, + output single_bitselect_res, + output [63:0] mul_res, + output [63:0] cat_res, + output [1:0] multiple_bitselect_res, + output [95:0] fill_res +); + assign add_res = x + y; + assign sub_res = x - y; + assign mod_res = x % y; + assign mul_res = x * y; + assign div_res = x / y; + assign equ_res = x == y; + assign not_equ_res = x != y; + assign and_res = x & y; + assign or_res = x | y; + assign xor_res = x ^ y; + assign not_res = ~x; + assign logical_not_res = !(x == 32'h0); + assign logical_and_res = x[0] && y[0]; + assign logical_or_res = x[0] || y[0]; + assign cat_res = {x,y}; + assign mux_res = c[0] ? x : y; + assign rshift_res = x >> y[2:0]; + assign lshift_res = x << y[2:0]; + assign gt_res = x > y; + assign lt_res = x < y; + assign geq_res = x >= y; + assign leq_res = x <= y; + assign single_bitselect_res = x[1]; + assign multiple_bitselect_res = x[1:0]; + assign fill_res = {3{x}}; + assign andR_res = &x; + assign orR_res = |x; + assign xorR_res = ^x; + + + + + +endmodule + +``` + +</td> +<td> + +```scala mdoc:silent +class OperatorExampleModule extends Module { + + val x, y, c = IO(Input(UInt(32.W))) + + val add_res, sub_res, + mod_res, div_res, and_res, + or_res, xor_res, not_res, + logical_not_res, mux_res, + rshift_res , lshift_res = IO(Output(UInt(32.W))) + + val logical_and_res, logical_or_res, + equ_res, not_equ_res, andR_res, + orR_res, xorR_res, gt_res,lt_res, + geq_res, leq_res,single_bitselect_res = IO(Output(Bool())) + + val mul_res, cat_res= IO(Output(UInt(64.W))) + + val multiple_bitselect_res = IO(Output(UInt(2.W))) + + val fill_res = IO(Output(UInt((3*32).W))) + + add_res := x + y + sub_res := x - y + mod_res := x % y + mul_res := x * y + div_res := x / y + equ_res := x === y + not_equ_res := x =/= y + and_res := x & y + or_res := x | y + xor_res := x ^ y + not_res := ~x + logical_not_res := !x + logical_and_res := x(0) && y(0) + logical_or_res := x(0) || y(0) + cat_res := Cat(x, y) + mux_res := Mux(c(0), x, y) + rshift_res := x >> y(2, 0) + lshift_res := x << y(2, 0) + gt_res := x > y + lt_res := x < y + geq_res := x >= y + leq_res := x <= y + single_bitselect_res := x(1) + multiple_bitselect_res := x(1, 0) + fill_res:= Fill(3,x) + andR_res := x.andR + orR_res := x.orR + xorR_res := x.xorR +} +``` + +```scala mdoc:invisible +ChiselStage.emitVerilog(new OperatorExampleModule) +``` +</td> + </tr> + </table> +</body> +</html> diff --git a/docs/src/explanations/connection-operators.md b/docs/src/explanations/connection-operators.md index 8a2117e1..86dca664 100644 --- a/docs/src/explanations/connection-operators.md +++ b/docs/src/explanations/connection-operators.md @@ -24,7 +24,7 @@ import chisel3.util.DecoupledIO ``` The diagram for the experiment can be viewed [here](https://docs.google.com/document/d/14C918Hdahk2xOGSJJBT-ZVqAx99_hg3JQIq-vaaifQU/edit?usp=sharing). - + ```scala mdoc:silent diff --git a/docs/src/images/connection-operators-experiment.svg b/docs/src/images/connection-operators-experiment.svg new file mode 100644 index 00000000..c163cddc --- /dev/null +++ b/docs/src/images/connection-operators-experiment.svg @@ -0,0 +1 @@ +<svg version="1.1" viewBox="0.0 0.0 800.0 600.0" fill="none" stroke="none" stroke-linecap="square" stroke-miterlimit="10" xmlns:xlink="http://www.w3.org/1999/xlink" xmlns="http://www.w3.org/2000/svg"><clipPath id="p.0"><path d="m0 0l800.0 0l0 600.0l-800.0 0l0 -600.0z" clip-rule="nonzero"/></clipPath><g clip-path="url(#p.0)"><path fill="#000000" fill-opacity="0.0" d="m0 0l800.0 0l0 600.0l-800.0 0z" fill-rule="evenodd"/><path fill="#cfe2f3" d="m55.574802 83.362206l523.84247 0l0 389.00787l-523.84247 0z" fill-rule="evenodd"/><path stroke="#000000" stroke-width="1.0" stroke-linejoin="round" stroke-linecap="butt" d="m55.574802 83.362206l523.84247 0l0 389.00787l-523.84247 0z" fill-rule="evenodd"/><path fill="#000000" fill-opacity="0.0" d="m199.65617 108.062996l592.78735 0l0 42.01574l-592.78735 0z" fill-rule="evenodd"/><path fill="#000000" d="m212.4218 134.98299l-3.53125 -13.359367l1.8125 0l2.03125 8.765617q0.328125 1.375 0.5625 2.71875q0.5 -2.140625 0.59375 -2.46875l2.546875 -9.015617l2.125 0l1.921875 6.7656174q0.71875 2.515625 1.03125 4.71875q0.265625 -1.265625 0.671875 -2.890625l2.09375 -8.593742l1.78125 0l-3.671875 13.359367l-1.703125 0l-2.8125 -10.171867q-0.359375 -1.28125 -0.421875 -1.5625q-0.203125 0.90625 -0.390625 1.5625l-2.828125 10.171867l-1.8125 0zm14.724548 0l0 -9.671867l1.46875 0l0 1.46875q0.5625 -1.03125 1.03125 -1.359375q0.484375 -0.328125 1.0625 -0.328125q0.828125 0 1.6875 0.53125l-0.5625 1.515625q-0.609375 -0.359375 -1.203125 -0.359375q-0.546875 0 -0.96875 0.328125q-0.421875 0.328125 -0.609375 0.890625q-0.28125 0.8749924 -0.28125 1.9218674l0 5.0625l-1.625 0zm12.540802 -1.1875q-0.921875 0.765625 -1.765625 1.09375q-0.828125 0.3125 -1.796875 0.3125q-1.59375 0 -2.453125 -0.78125q-0.859375 -0.78125 -0.859375 -1.984375q0 -0.71875 0.328125 -1.296875q0.328125 -0.59375 0.84375 -0.9375q0.53125 -0.359375 1.1875 -0.546875q0.46875 -0.125 1.453125 -0.25q1.984375 -0.234375 2.921875 -0.5625q0.015625 -0.34375 0.015625 -0.421875q0 -0.9999924 -0.46875 -1.4218674q-0.625 -0.546875 -1.875 -0.546875q-1.15625 0 -1.703125 0.40625q-0.546875 0.40625 -0.8125 1.4218674l-1.609375 -0.21875q0.21875 -1.0156174 0.71875 -1.6406174q0.5 -0.640625 1.453125 -0.984375q0.953125 -0.34375 2.1875 -0.34375q1.25 0 2.015625 0.296875q0.78125 0.28125 1.140625 0.734375q0.375 0.4375 0.515625 1.109375q0.078125 0.421875 0.078125 1.5156174l0 2.1875q0 2.28125 0.109375 2.890625q0.109375 0.59375 0.40625 1.15625l-1.703125 0q-0.265625 -0.515625 -0.328125 -1.1875zm-0.140625 -3.671875q-0.890625 0.375 -2.671875 0.625q-1.015625 0.140625 -1.4375 0.328125q-0.421875 0.1875 -0.65625 0.53125q-0.21875 0.34375 -0.21875 0.78125q0 0.65625 0.5 1.09375q0.5 0.4375 1.453125 0.4375q0.9375 0 1.671875 -0.40625q0.75 -0.421875 1.09375 -1.140625q0.265625 -0.5625 0.265625 -1.640625l0 -0.609375zm4.203842 8.5625l0 -13.374992l1.484375 0l0 1.25q0.53125 -0.734375 1.1875 -1.09375q0.671875 -0.375 1.625 -0.375q1.234375 0 2.171875 0.640625q0.953125 0.625 1.4375 1.796875q0.484375 1.1562424 0.484375 2.5468674q0 1.484375 -0.53125 2.671875q-0.53125 1.1875 -1.546875 1.828125q-1.015625 0.625 -2.140625 0.625q-0.8125 0 -1.46875 -0.34375q-0.65625 -0.34375 -1.0625 -0.875l0 4.703125l-1.640625 0zm1.484375 -8.484375q0 1.859375 0.75 2.765625q0.765625 0.890625 1.828125 0.890625q1.09375 0 1.875 -0.921875q0.78125 -0.9375 0.78125 -2.875q0 -1.84375 -0.765625 -2.7656174q-0.75 -0.921875 -1.8125 -0.921875q-1.046875 0 -1.859375 0.984375q-0.796875 0.9687424 -0.796875 2.8437424zm8.891342 8.484375l0 -13.374992l1.484375 0l0 1.25q0.53123474 -0.734375 1.1874847 -1.09375q0.671875 -0.375 1.625 -0.375q1.234375 0 2.171875 0.640625q0.953125 0.625 1.4375 1.796875q0.484375 1.1562424 0.484375 2.5468674q0 1.484375 -0.53125 2.671875q-0.53125 1.1875 -1.546875 1.828125q-1.015625 0.625 -2.140625 0.625q-0.8125 0 -1.46875 -0.34375q-0.65625 -0.34375 -1.0624847 -0.875l0 4.703125l-1.640625 0zm1.484375 -8.484375q0 1.859375 0.74998474 2.765625q0.765625 0.890625 1.828125 0.890625q1.09375 0 1.875 -0.921875q0.78125 -0.9375 0.78125 -2.875q0 -1.84375 -0.765625 -2.7656174q-0.75 -0.921875 -1.8125 -0.921875q-1.046875 0 -1.859375 0.984375q-0.79685974 0.9687424 -0.79685974 2.8437424zm15.516342 1.671875l1.6875 0.203125q-0.40625 1.484375 -1.484375 2.3125q-1.078125 0.8125 -2.765625 0.8125q-2.125 0 -3.375 -1.296875q-1.234375 -1.3125 -1.234375 -3.671875q0 -2.4531174 1.25 -3.7968674q1.265625 -1.34375 3.265625 -1.34375q1.9375 0 3.15625 1.328125q1.234375 1.3125 1.234375 3.7031174q0 0.15625 0 0.4375l-7.21875 0q0.09375 1.59375 0.90625 2.453125q0.8125 0.84375 2.015625 0.84375q0.90625 0 1.546875 -0.46875q0.640625 -0.484375 1.015625 -1.515625zm-5.390625 -2.65625l5.40625 0q-0.109375 -1.2187424 -0.625 -1.8281174q-0.78125 -0.953125 -2.03125 -0.953125q-1.125 0 -1.90625 0.765625q-0.765625 0.75 -0.84375 2.0156174zm9.125702 5.765625l0 -9.671867l1.46875 0l0 1.46875q0.5625 -1.03125 1.03125 -1.359375q0.484375 -0.328125 1.0625 -0.328125q0.828125 0 1.6875 0.53125l-0.5625 1.515625q-0.609375 -0.359375 -1.203125 -0.359375q-0.546875 0 -0.96875 0.328125q-0.421875 0.328125 -0.609375 0.890625q-0.28125 0.8749924 -0.28125 1.9218674l0 5.0625l-1.625 0z" fill-rule="nonzero"/><path fill="#cfe2f3" d="m120.41207 225.38583l143.05511 0l0 152.31494l-143.05511 0z" fill-rule="evenodd"/><path stroke="#000000" stroke-width="1.0" stroke-linejoin="round" stroke-linecap="butt" d="m120.41207 225.38583l143.05511 0l0 152.31494l-143.05511 0z" fill-rule="evenodd"/><path fill="#000000" d="m130.84958 363.46332l0 -13.359375l5.046875 0q1.328125 0 2.03125 0.125q0.96875 0.171875 1.640625 0.640625q0.671875 0.453125 1.078125 1.28125q0.40625 0.828125 0.40625 1.828125q0 1.703125 -1.09375 2.890625q-1.078125 1.171875 -3.921875 1.171875l-3.421875 0l0 5.421875l-1.765625 0zm1.765625 -7.0l3.453125 0q1.71875 0 2.4375 -0.640625q0.71875 -0.640625 0.71875 -1.796875q0 -0.84375 -0.421875 -1.4375q-0.421875 -0.59375 -1.125 -0.78125q-0.4375 -0.125 -1.640625 -0.125l-3.421875 0l0 4.78125zm10.459198 7.0l0 -9.671875l1.46875 0l0 1.46875q0.5625 -1.03125 1.03125 -1.359375q0.484375 -0.328125 1.0625 -0.328125q0.828125 0 1.6875 0.53125l-0.5625 1.515625q-0.609375 -0.359375 -1.203125 -0.359375q-0.546875 0 -0.96875 0.328125q-0.421875 0.328125 -0.609375 0.890625q-0.28125 0.875 -0.28125 1.921875l0 5.0625l-1.625 0zm5.618927 -4.84375q0 -2.6875 1.484375 -3.96875q1.25 -1.078125 3.046875 -1.078125q2.0 0 3.265625 1.3125q1.265625 1.296875 1.265625 3.609375q0 1.859375 -0.5625 2.9375q-0.5625 1.0625 -1.640625 1.65625q-1.0625 0.59375 -2.328125 0.59375q-2.03125 0 -3.28125 -1.296875q-1.25 -1.3125 -1.25 -3.765625zm1.6875 0q0 1.859375 0.796875 2.796875q0.8125 0.921875 2.046875 0.921875q1.21875 0 2.03125 -0.921875q0.8125 -0.9375 0.8125 -2.84375q0 -1.796875 -0.8125 -2.71875q-0.8125 -0.921875 -2.03125 -0.921875q-1.234375 0 -2.046875 0.921875q-0.796875 0.90625 -0.796875 2.765625zm15.563217 4.84375l0 -1.21875q-0.90625 1.4375 -2.703125 1.4375q-1.15625 0 -2.125 -0.640625q-0.96875 -0.640625 -1.5 -1.78125q-0.53125 -1.140625 -0.53125 -2.625q0 -1.453125 0.484375 -2.625q0.484375 -1.1875 1.4375 -1.8125q0.96875 -0.625 2.171875 -0.625q0.875 0 1.546875 0.375q0.6875 0.359375 1.109375 0.953125l0 -4.796875l1.640625 0l0 13.359375l-1.53125 0zm-5.171875 -4.828125q0 1.859375 0.78125 2.78125q0.78125 0.921875 1.84375 0.921875q1.078125 0 1.828125 -0.875q0.75 -0.890625 0.75 -2.6875q0 -1.984375 -0.765625 -2.90625q-0.765625 -0.9375 -1.890625 -0.9375q-1.078125 0 -1.8125 0.890625q-0.734375 0.890625 -0.734375 2.8125zm15.610092 4.828125l0 -1.421875q-1.125 1.640625 -3.0625 1.640625q-0.859375 0 -1.609375 -0.328125q-0.734375 -0.328125 -1.09375 -0.828125q-0.359375 -0.5 -0.5 -1.21875q-0.109375 -0.46875 -0.109375 -1.53125l0 -5.984375l1.640625 0l0 5.359375q0 1.28125 0.109375 1.734375q0.15625 0.640625 0.65625 1.015625q0.5 0.375 1.234375 0.375q0.734375 0 1.375 -0.375q0.65625 -0.390625 0.921875 -1.03125q0.265625 -0.65625 0.265625 -1.890625l0 -5.1875l1.640625 0l0 9.671875l-1.46875 0zm10.360092 -3.546875l1.609375 0.21875q-0.265625 1.65625 -1.359375 2.609375q-1.078125 0.9375 -2.671875 0.9375q-1.984375 0 -3.1875 -1.296875q-1.203125 -1.296875 -1.203125 -3.71875q0 -1.578125 0.515625 -2.75q0.515625 -1.171875 1.578125 -1.75q1.0625 -0.59375 2.3125 -0.59375q1.578125 0 2.578125 0.796875q1.0 0.796875 1.28125 2.265625l-1.59375 0.234375q-0.234375 -0.96875 -0.8125 -1.453125q-0.578125 -0.5 -1.390625 -0.5q-1.234375 0 -2.015625 0.890625q-0.78125 0.890625 -0.78125 2.8125q0 1.953125 0.75 2.84375q0.75 0.875 1.953125 0.875q0.96875 0 1.609375 -0.59375q0.65625 -0.59375 0.828125 -1.828125zm9.640625 0.4375l1.6875 0.203125q-0.40625 1.484375 -1.484375 2.3125q-1.078125 0.8125 -2.765625 0.8125q-2.125 0 -3.375 -1.296875q-1.234375 -1.3125 -1.234375 -3.671875q0 -2.453125 1.25 -3.796875q1.265625 -1.34375 3.265625 -1.34375q1.9375 0 3.15625 1.328125q1.234375 1.3125 1.234375 3.703125q0 0.15625 0 0.4375l-7.21875 0q0.09375 1.59375 0.90625 2.453125q0.8125 0.84375 2.015625 0.84375q0.90625 0 1.546875 -0.46875q0.640625 -0.484375 1.015625 -1.515625zm-5.390625 -2.65625l5.40625 0q-0.109375 -1.21875 -0.625 -1.828125q-0.78125 -0.953125 -2.03125 -0.953125q-1.125 0 -1.90625 0.765625q-0.765625 0.75 -0.84375 2.015625zm9.125717 5.765625l0 -9.671875l1.46875 0l0 1.46875q0.5625 -1.03125 1.03125 -1.359375q0.484375 -0.328125 1.0625 -0.328125q0.828125 0 1.6875 0.53125l-0.5625 1.515625q-0.609375 -0.359375 -1.203125 -0.359375q-0.546875 0 -0.96875 0.328125q-0.421875 0.328125 -0.609375 0.890625q-0.28125 0.875 -0.28125 1.921875l0 5.0625l-1.625 0z" fill-rule="nonzero"/><path fill="#cfe2f3" d="m374.14697 223.84251l143.05511 0l0 152.31496l-143.05511 0z" fill-rule="evenodd"/><path stroke="#000000" stroke-width="1.0" stroke-linejoin="round" stroke-linecap="butt" d="m374.14697 223.84251l143.05511 0l0 152.31496l-143.05511 0z" fill-rule="evenodd"/><path fill="#000000" d="m394.11572 357.2325l1.765625 0.453125q-0.5625 2.171875 -2.0 3.328125q-1.4375 1.140625 -3.53125 1.140625q-2.15625 0 -3.515625 -0.875q-1.34375 -0.890625 -2.0625 -2.546875q-0.703125 -1.671875 -0.703125 -3.59375q0 -2.078125 0.796875 -3.625q0.796875 -1.5625 2.265625 -2.359375q1.484375 -0.8125 3.25 -0.8125q2.0 0 3.359375 1.015625q1.375 1.015625 1.90625 2.875l-1.734375 0.40625q-0.46875 -1.453125 -1.359375 -2.109375q-0.875 -0.671875 -2.203125 -0.671875q-1.546875 0 -2.578125 0.734375q-1.03125 0.734375 -1.453125 1.984375q-0.421875 1.234375 -0.421875 2.5625q0 1.703125 0.5 2.96875q0.5 1.265625 1.546875 1.90625q1.046875 0.625 2.265625 0.625q1.484375 0 2.515625 -0.859375q1.03125 -0.859375 1.390625 -2.546875zm3.1292114 -0.15625q0 -2.6875 1.484375 -3.96875q1.25 -1.078125 3.046875 -1.078125q2.0 0 3.265625 1.3125q1.265625 1.296875 1.265625 3.609375q0 1.859375 -0.5625 2.9375q-0.5625 1.0625 -1.640625 1.65625q-1.0625 0.59375 -2.328125 0.59375q-2.03125 0 -3.28125 -1.296875q-1.25 -1.3125 -1.25 -3.765625zm1.6875 0q0 1.859375 0.796875 2.796875q0.8125 0.921875 2.046875 0.921875q1.21875 0 2.03125 -0.921875q0.8125 -0.9375 0.8125 -2.84375q0 -1.796875 -0.8125 -2.71875q-0.8125 -0.921875 -2.03125 -0.921875q-1.234375 0 -2.046875 0.921875q-0.796875 0.90625 -0.796875 2.765625zm9.297577 4.84375l0 -9.671875l1.46875 0l0 1.375q1.0625 -1.59375 3.078125 -1.59375q0.875 0 1.609375 0.3125q0.734375 0.3125 1.09375 0.828125q0.375 0.5 0.515625 1.203125q0.09375 0.453125 0.09375 1.59375l0 5.953125l-1.640625 0l0 -5.890625q0 -1.0 -0.203125 -1.484375q-0.1875 -0.5 -0.671875 -0.796875q-0.484375 -0.296875 -1.140625 -0.296875q-1.046875 0 -1.8125 0.671875q-0.75 0.65625 -0.75 2.515625l0 5.28125l-1.640625 0zm9.719482 -2.890625l1.625 -0.25q0.125 0.96875 0.75 1.5q0.625 0.515625 1.75 0.515625q1.125 0 1.671875 -0.453125q0.546875 -0.46875 0.546875 -1.09375q0 -0.546875 -0.484375 -0.875q-0.328125 -0.21875 -1.671875 -0.546875q-1.8125 -0.46875 -2.515625 -0.796875q-0.6875 -0.328125 -1.046875 -0.90625q-0.359375 -0.59375 -0.359375 -1.3125q0 -0.640625 0.296875 -1.1875q0.296875 -0.5625 0.8125 -0.921875q0.375 -0.28125 1.03125 -0.46875q0.671875 -0.203125 1.421875 -0.203125q1.140625 0 2.0 0.328125q0.859375 0.328125 1.265625 0.890625q0.421875 0.5625 0.578125 1.5l-1.609375 0.21875q-0.109375 -0.75 -0.640625 -1.171875q-0.515625 -0.421875 -1.46875 -0.421875q-1.140625 0 -1.625 0.375q-0.46875 0.375 -0.46875 0.875q0 0.3125 0.1875 0.578125q0.203125 0.265625 0.640625 0.4375q0.234375 0.09375 1.4375 0.421875q1.75 0.453125 2.4375 0.75q0.6875 0.296875 1.078125 0.859375q0.390625 0.5625 0.390625 1.40625q0 0.828125 -0.484375 1.546875q-0.46875 0.71875 -1.375 1.125q-0.90625 0.390625 -2.046875 0.390625q-1.875 0 -2.875 -0.78125q-0.984375 -0.78125 -1.25 -2.328125zm16.3125 2.890625l0 -1.421875q-1.125 1.640625 -3.0625 1.640625q-0.859375 0 -1.609375 -0.328125q-0.734375 -0.328125 -1.09375 -0.828125q-0.359375 -0.5 -0.5 -1.21875q-0.109375 -0.46875 -0.109375 -1.53125l0 -5.984375l1.640625 0l0 5.359375q0 1.28125 0.109375 1.734375q0.15625 0.640625 0.65625 1.015625q0.5 0.375 1.234375 0.375q0.734375 0 1.375 -0.375q0.65625 -0.390625 0.921875 -1.03125q0.265625 -0.65625 0.265625 -1.890625l0 -5.1875l1.640625 0l0 9.671875l-1.46875 0zm4.047577 0l0 -9.671875l1.46875 0l0 1.359375q0.453125 -0.71875 1.203125 -1.140625q0.765625 -0.4375 1.71875 -0.4375q1.078125 0 1.765625 0.453125q0.6875 0.4375 0.96875 1.234375q1.15625 -1.6875 2.984375 -1.6875q1.453125 0 2.21875 0.796875q0.78125 0.796875 0.78125 2.453125l0 6.640625l-1.640625 0l0 -6.09375q0 -0.984375 -0.15625 -1.40625q-0.15625 -0.4375 -0.578125 -0.703125q-0.421875 -0.265625 -0.984375 -0.265625q-1.015625 0 -1.6875 0.6875q-0.671875 0.671875 -0.671875 2.15625l0 5.625l-1.640625 0l0 -6.28125q0 -1.09375 -0.40625 -1.640625q-0.40625 -0.546875 -1.3125 -0.546875q-0.6875 0 -1.28125 0.359375q-0.59375 0.359375 -0.859375 1.0625q-0.25 0.703125 -0.25 2.03125l0 5.015625l-1.640625 0zm22.165802 -3.109375l1.6875 0.203125q-0.40625 1.484375 -1.484375 2.3125q-1.078125 0.8125 -2.765625 0.8125q-2.125 0 -3.375 -1.296875q-1.234375 -1.3125 -1.234375 -3.671875q0 -2.453125 1.25 -3.796875q1.265625 -1.34375 3.265625 -1.34375q1.9375 0 3.15625 1.328125q1.234375 1.3125 1.234375 3.703125q0 0.15625 0 0.4375l-7.21875 0q0.09375 1.59375 0.90625 2.453125q0.8125 0.84375 2.015625 0.84375q0.90625 0 1.546875 -0.46875q0.640625 -0.484375 1.015625 -1.515625zm-5.390625 -2.65625l5.40625 0q-0.109375 -1.21875 -0.625 -1.828125q-0.78125 -0.953125 -2.03125 -0.953125q-1.125 0 -1.90625 0.765625q-0.765625 0.75 -0.84375 2.015625zm9.125732 5.765625l0 -9.671875l1.46875 0l0 1.46875q0.5625 -1.03125 1.03125 -1.359375q0.484375 -0.328125 1.0625 -0.328125q0.828125 0 1.6875 0.53125l-0.5625 1.515625q-0.609375 -0.359375 -1.203125 -0.359375q-0.546875 0 -0.96875 0.328125q-0.421875 0.328125 -0.609375 0.890625q-0.28125 0.875 -0.28125 1.921875l0 5.0625l-1.625 0z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m55.574802 277.86615l64.85039 23.685028" fill-rule="evenodd"/><path stroke="#000000" stroke-width="1.0" stroke-linejoin="round" stroke-linecap="butt" d="m55.574802 277.86615l59.21452 21.626678" fill-rule="evenodd"/><path fill="#000000" stroke="#000000" stroke-width="1.0" stroke-linecap="butt" d="m114.22267 301.0443l4.829338 0.005340576l-3.696045 -3.1083374z" fill-rule="evenodd"/><path fill="#000000" fill-opacity="0.0" d="m263.5643 293.85828l110.58267 6.1417236" fill-rule="evenodd"/><path stroke="#000000" stroke-width="1.0" stroke-linejoin="round" stroke-linecap="butt" d="m263.5643 293.85828l104.59192 5.8089905" fill-rule="evenodd"/><path fill="#000000" stroke="#000000" stroke-width="1.0" stroke-linecap="butt" d="m368.0646 301.31647l4.622711 -1.397522l-4.439514 -1.9008484z" fill-rule="evenodd"/><path fill="#000000" fill-opacity="0.0" d="m517.2126 301.55118l62.204712 -23.685028" fill-rule="evenodd"/><path stroke="#000000" stroke-width="1.0" stroke-linejoin="round" stroke-linecap="butt" d="m517.2126 301.55118l56.597473 -21.550018" fill-rule="evenodd"/><path fill="#000000" stroke="#000000" stroke-width="1.0" stroke-linecap="butt" d="m574.39777 281.5448l3.6533203 -3.1584473l-4.8287964 0.07119751z" fill-rule="evenodd"/><path fill="#000000" fill-opacity="0.0" d="m579.4173 256.85828l592.7874 0l0 42.015747l-592.7874 0z" fill-rule="evenodd"/><path fill="#000000" d="m589.0423 278.9345q0 -2.6875 1.484375 -3.96875q1.25 -1.078125 3.046875 -1.078125q2.0 0 3.265625 1.3125q1.265625 1.296875 1.265625 3.609375q0 1.859375 -0.5625 2.9375q-0.5625 1.0625 -1.640625 1.65625q-1.0625 0.59375 -2.328125 0.59375q-2.03125 0 -3.28125 -1.296875q-1.25 -1.3125 -1.25 -3.765625zm1.6875 0q0 1.859375 0.796875 2.796875q0.8125 0.921875 2.046875 0.921875q1.21875 0 2.03125 -0.921875q0.8125 -0.9375 0.8125 -2.84375q0 -1.796875 -0.8125 -2.71875q-0.8125 -0.921875 -2.03125 -0.921875q-1.234375 0 -2.046875 0.921875q-0.796875 0.90625 -0.796875 2.765625zm15.625732 4.84375l0 -1.421875q-1.125 1.640625 -3.0625 1.640625q-0.859375 0 -1.609375 -0.328125q-0.734375 -0.328125 -1.09375 -0.828125q-0.359375 -0.5 -0.5 -1.21875q-0.109375 -0.46875 -0.109375 -1.53125l0 -5.984375l1.640625 0l0 5.359375q0 1.28125 0.109375 1.734375q0.15625 0.640625 0.65625 1.015625q0.5 0.375 1.234375 0.375q0.734375 0 1.375 -0.375q0.65625 -0.390625 0.921875 -1.03125q0.265625 -0.65625 0.265625 -1.890625l0 -5.1875l1.640625 0l0 9.671875l-1.46875 0zm7.6257324 -1.46875l0.234375 1.453125q-0.6875 0.140625 -1.234375 0.140625q-0.890625 0 -1.390625 -0.28125q-0.484375 -0.28125 -0.6875 -0.734375q-0.203125 -0.46875 -0.203125 -1.9375l0 -5.578125l-1.203125 0l0 -1.265625l1.203125 0l0 -2.390625l1.625 -0.984375l0 3.375l1.65625 0l0 1.265625l-1.65625 0l0 5.671875q0 0.6875 0.078125 0.890625q0.09375 0.203125 0.28125 0.328125q0.203125 0.109375 0.578125 0.109375q0.265625 0 0.71875 -0.0625z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m14.971128 245.07086l592.7874 0l0 42.015747l-592.7874 0z" fill-rule="evenodd"/><path fill="#000000" d="m25.205503 260.52213l0 -1.890625l1.640625 0l0 1.890625l-1.640625 0zm0 11.46875l0 -9.671875l1.640625 0l0 9.671875l-1.640625 0zm4.144821 0l0 -9.671875l1.46875 0l0 1.375q1.0625 -1.59375 3.078127 -1.59375q0.875 0 1.609375 0.3125q0.734375 0.3125 1.09375 0.828125q0.375 0.5 0.515625 1.203125q0.09375 0.453125 0.09375 1.59375l0 5.953125l-1.640625 0l0 -5.890625q0 -1.0 -0.203125 -1.484375q-0.1875 -0.5 -0.671875 -0.796875q-0.484375 -0.296875 -1.140625 -0.296875q-1.046875 0 -1.8125019 0.671875q-0.75 0.65625 -0.75 2.515625l0 5.28125l-1.640625 0z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m120.42519 277.55118l39.02363 0l0 42.015747l-39.02363 0z" fill-rule="evenodd"/><path fill="#000000" d="m130.65958 293.00244l0 -1.890625l1.640625 0l0 1.890625l-1.640625 0zm0 11.46875l0 -9.671875l1.640625 0l0 9.671875l-1.640625 0zm4.144821 0l0 -9.671875l1.46875 0l0 1.375q1.0625 -1.59375 3.078125 -1.59375q0.875 0 1.609375 0.3125q0.734375 0.3125 1.09375 0.828125q0.375 0.5 0.515625 1.203125q0.09375 0.453125 0.09375 1.59375l0 5.953125l-1.640625 0l0 -5.890625q0 -1.0 -0.203125 -1.484375q-0.1875 -0.5 -0.671875 -0.796875q-0.484375 -0.296875 -1.140625 -0.296875q-1.046875 0 -1.8125 0.671875q-0.75 0.65625 -0.75 2.515625l0 5.28125l-1.640625 0z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m374.14697 314.12073l34.4252 0l0 42.015747l-34.4252 0z" fill-rule="evenodd"/><path fill="#000000" d="m384.38135 329.572l0 -1.890625l1.640625 0l0 1.890625l-1.640625 0zm0 11.46875l0 -9.671875l1.640625 0l0 9.671875l-1.640625 0zm4.1448364 0l0 -9.671875l1.46875 0l0 1.375q1.0625 -1.59375 3.078125 -1.59375q0.875 0 1.609375 0.3125q0.734375 0.3125 1.09375 0.828125q0.375 0.5 0.515625 1.203125q0.09375 0.453125 0.09375 1.59375l0 5.953125l-1.640625 0l0 -5.890625q0 -1.0 -0.203125 -1.484375q-0.1875 -0.5 -0.671875 -0.796875q-0.484375 -0.296875 -1.140625 -0.296875q-1.046875 0 -1.8125 0.671875q-0.75 0.65625 -0.75 2.515625l0 5.28125l-1.640625 0z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m216.24803 269.55118l55.2126 0l0 42.015747l-55.2126 0z" fill-rule="evenodd"/><path fill="#000000" d="m225.87303 291.62744q0 -2.6875 1.484375 -3.96875q1.25 -1.078125 3.046875 -1.078125q2.0 0 3.265625 1.3125q1.265625 1.296875 1.265625 3.609375q0 1.859375 -0.5625 2.9375q-0.5625 1.0625 -1.640625 1.65625q-1.0625 0.59375 -2.328125 0.59375q-2.03125 0 -3.28125 -1.296875q-1.25 -1.3125 -1.25 -3.765625zm1.6875 0q0 1.859375 0.796875 2.796875q0.8125 0.921875 2.046875 0.921875q1.21875 0 2.03125 -0.921875q0.8125 -0.9375 0.8125 -2.84375q0 -1.796875 -0.8125 -2.71875q-0.8125 -0.921875 -2.03125 -0.921875q-1.234375 0 -2.046875 0.921875q-0.796875 0.90625 -0.796875 2.765625zm15.625717 4.84375l0 -1.421875q-1.125 1.640625 -3.0625 1.640625q-0.859375 0 -1.609375 -0.328125q-0.734375 -0.328125 -1.09375 -0.828125q-0.359375 -0.5 -0.5 -1.21875q-0.109375 -0.46875 -0.109375 -1.53125l0 -5.984375l1.640625 0l0 5.359375q0 1.28125 0.109375 1.734375q0.15625 0.640625 0.65625 1.015625q0.5 0.375 1.234375 0.375q0.734375 0 1.375 -0.375q0.65625 -0.390625 0.921875 -1.03125q0.265625 -0.65625 0.265625 -1.890625l0 -5.1875l1.640625 0l0 9.671875l-1.46875 0zm7.625717 -1.46875l0.234375 1.453125q-0.6875 0.140625 -1.234375 0.140625q-0.890625 0 -1.390625 -0.28125q-0.484375 -0.28125 -0.6875 -0.734375q-0.203125 -0.46875 -0.203125 -1.9375l0 -5.578125l-1.203125 0l0 -1.265625l1.203125 0l0 -2.390625l1.625 -0.984375l0 3.375l1.65625 0l0 1.265625l-1.65625 0l0 5.671875q0 0.6875 0.078125 0.890625q0.09375 0.203125 0.28125 0.328125q0.203125 0.109375 0.578125 0.109375q0.265625 0 0.71875 -0.0625z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m368.4252 277.55118l39.02362 0l0 42.015747l-39.02362 0z" fill-rule="evenodd"/><path fill="#000000" d="m378.65958 293.00244l0 -1.890625l1.640625 0l0 1.890625l-1.640625 0zm0 11.46875l0 -9.671875l1.640625 0l0 9.671875l-1.640625 0zm4.144806 0l0 -9.671875l1.46875 0l0 1.375q1.0625 -1.59375 3.078125 -1.59375q0.875 0 1.609375 0.3125q0.734375 0.3125 1.09375 0.828125q0.375 0.5 0.515625 1.203125q0.09375 0.453125 0.09375 1.59375l0 5.953125l-1.640625 0l0 -5.890625q0 -1.0 -0.203125 -1.484375q-0.1875 -0.5 -0.671875 -0.796875q-0.484375 -0.296875 -1.140625 -0.296875q-1.046875 0 -1.8125 0.671875q-0.75 0.65625 -0.75 2.515625l0 5.28125l-1.640625 0z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m478.26248 277.55118l49.196808 0l0 42.015747l-49.196808 0z" fill-rule="evenodd"/><path fill="#000000" d="m487.88748 299.62744q0 -2.6875 1.484375 -3.96875q1.25 -1.078125 3.046875 -1.078125q2.0 0 3.265625 1.3125q1.265625 1.296875 1.265625 3.609375q0 1.859375 -0.5625 2.9375q-0.5625 1.0625 -1.640625 1.65625q-1.0625 0.59375 -2.328125 0.59375q-2.03125 0 -3.28125 -1.296875q-1.25 -1.3125 -1.25 -3.765625zm1.6875 0q0 1.859375 0.796875 2.796875q0.8125 0.921875 2.046875 0.921875q1.21875 0 2.03125 -0.921875q0.8125 -0.9375 0.8125 -2.84375q0 -1.796875 -0.8125 -2.71875q-0.8125 -0.921875 -2.03125 -0.921875q-1.234375 0 -2.046875 0.921875q-0.796875 0.90625 -0.796875 2.765625zm15.625702 4.84375l0 -1.421875q-1.125 1.640625 -3.0625 1.640625q-0.859375 0 -1.609375 -0.328125q-0.734375 -0.328125 -1.09375 -0.828125q-0.359375 -0.5 -0.5 -1.21875q-0.109375 -0.46875 -0.109375 -1.53125l0 -5.984375l1.640625 0l0 5.359375q0 1.28125 0.109375 1.734375q0.15625 0.640625 0.65625 1.015625q0.5 0.375 1.234375 0.375q0.734375 0 1.375 -0.375q0.65625 -0.390625 0.921875 -1.03125q0.265625 -0.65625 0.265625 -1.890625l0 -5.1875l1.640625 0l0 9.671875l-1.46875 0zm7.6257324 -1.46875l0.234375 1.453125q-0.6875 0.140625 -1.234375 0.140625q-0.890625 0 -1.390625 -0.28125q-0.484375 -0.28125 -0.6875 -0.734375q-0.203125 -0.46875 -0.203125 -1.9375l0 -5.578125l-1.203125 0l0 -1.265625l1.203125 0l0 -2.390625l1.625 -0.984375l0 3.375l1.65625 0l0 1.265625l-1.65625 0l0 5.671875q0 0.6875 0.078125 0.890625q0.09375 0.203125 0.28125 0.328125q0.203125 0.109375 0.578125 0.109375q0.265625 0 0.71875 -0.0625z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m72.24803 253.55118l55.2126 0l0 42.015747l-55.2126 0z" fill-rule="evenodd"/><path fill="#000000" d="m81.21678 280.4712l5.125 -13.359375l1.90625 0l5.46875 13.359375l-2.015625 0l-1.546875 -4.046875l-5.59375 0l-1.46875 4.046875l-1.875 0zm3.859375 -5.484375l4.53125 0l-1.40625 -3.703125q-0.625 -1.6875 -0.9375 -2.765625q-0.265625 1.28125 -0.71875 2.546875l-1.46875 3.921875z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m288.3386 256.85828l55.212585 0l0 42.015747l-55.212585 0z" fill-rule="evenodd"/><path fill="#000000" d="m298.69797 283.77826l0 -13.359375l5.015625 0q1.53125 0 2.453125 0.40625q0.921875 0.40625 1.4375 1.25q0.53125 0.84375 0.53125 1.765625q0 0.859375 -0.46875 1.625q-0.453125 0.75 -1.390625 1.203125q1.203125 0.359375 1.859375 1.21875q0.65625 0.859375 0.65625 2.015625q0 0.9375 -0.40625 1.75q-0.390625 0.796875 -0.984375 1.234375q-0.578125 0.4375 -1.453125 0.671875q-0.875 0.21875 -2.15625 0.21875l-5.09375 0zm1.78125 -7.75l2.875 0q1.1875 0 1.6875 -0.140625q0.671875 -0.203125 1.015625 -0.671875q0.34375 -0.46875 0.34375 -1.171875q0 -0.65625 -0.328125 -1.15625q-0.3125 -0.515625 -0.90625 -0.703125q-0.59375 -0.1875 -2.03125 -0.1875l-2.65625 0l0 4.03125zm0 6.171875l3.3125 0q0.859375 0 1.203125 -0.0625q0.609375 -0.109375 1.015625 -0.359375q0.421875 -0.265625 0.6875 -0.75q0.265625 -0.484375 0.265625 -1.125q0 -0.75 -0.390625 -1.296875q-0.375 -0.546875 -1.0625 -0.765625q-0.671875 -0.234375 -1.953125 -0.234375l-3.078125 0l0 4.59375z" fill-rule="nonzero"/><path fill="#000000" fill-opacity="0.0" d="m528.33856 256.85828l55.212646 0l0 42.015747l-55.212646 0z" fill-rule="evenodd"/><path fill="#000000" d="m538.69794 283.77826l0 -13.359375l5.015625 0q1.53125 0 2.453125 0.40625q0.921875 0.40625 1.4375 1.25q0.53125 0.84375 0.53125 1.765625q0 0.859375 -0.46875 1.625q-0.453125 0.75 -1.390625 1.203125q1.203125 0.359375 1.859375 1.21875q0.65625 0.859375 0.65625 2.015625q0 0.9375 -0.40625 1.75q-0.390625 0.796875 -0.984375 1.234375q-0.578125 0.4375 -1.453125 0.671875q-0.875 0.21875 -2.15625 0.21875l-5.09375 0zm1.78125 -7.75l2.875 0q1.1875 0 1.6875 -0.140625q0.671875 -0.203125 1.015625 -0.671875q0.34375 -0.46875 0.34375 -1.171875q0 -0.65625 -0.328125 -1.15625q-0.3125 -0.515625 -0.90625 -0.703125q-0.59375 -0.1875 -2.03125 -0.1875l-2.65625 0l0 4.03125zm0 6.171875l3.3125 0q0.859375 0 1.203125 -0.0625q0.609375 -0.109375 1.015625 -0.359375q0.421875 -0.265625 0.6875 -0.75q0.265625 -0.484375 0.265625 -1.125q0 -0.75 -0.390625 -1.296875q-0.375 -0.546875 -1.0625 -0.765625q-0.671875 -0.234375 -1.953125 -0.234375l-3.078125 0l0 4.59375z" fill-rule="nonzero"/></g></svg> |